In Space No One Can Hear Electronics Scream

By Warren Miller, Mouser Electronics

Where Does Space Start?

Outer space is generally considered to be the void between planets, stars, and other celestial bodies. Deep space isn’t empty, but it does start with a hard vacuum containing perhaps a single hydrogen or helium atom per cubic meter. Also found in that cubic meter are electromagnetic radiation, magnetic fields, neutrinos, dust, and cosmic rays. Closer to the Earth’s atmosphere, where particle density increases, highly energetic particles like alpha, beta, and gamma rays can be created. These rays can even find their way down to sea level, but at much less density than in the upper atmosphere.

There is no specific distance at which space begins, since the atmosphere just gradually gets thinner as one gets further from Earth. However, there are a few “rules of thumb:” Most treaties that cover outer space-related issues use the Kármán line, at 100 km above sea level, as the start of outer space. This altitude is a convenient demarcation line between aeronautics and astronautics because a winged vehicle would have to travel faster than the orbital velocity in order to generate enough lift to support itself.

- The United States designates anyone who travels higher than 50 km above sea level as an astronaut.

- The human body needs a pressure suit to survive higher than about 20 km above sea level, where the atmospheric pressure is low enough that liquids in an exposed human body will boil away.

- Charged particles in space reach a midpoint of severity at around 120 km above sea level making this a convenient boundary between the harsh environment of space and the more protected area of the upper atmosphere.

Featured Products

Featured Suppliers

Featured Resources

Space is one of the harshest environments you can imagine for human beings – even without monstrous alien predators. Pressure, or the lack of it, temperature, or the lack of it, high-energy particles, and radiation are just not very human-friendly. Space is also one of the most difficult environments in which to design electronics systems. Space electronics components need to be able to withstand an almost perfect vacuum and operate at extremes of temperature. Power can be at a real premium in space exploration too – there are no long extension cords – so low power operation is often a necessity. And, of course, high-energy particles that can “flip” bits stored in an SRAM used to house MCU code or used to configure the logic in an FPGA can create logic errors that could lead to a failure, perhaps one that incorrectly blows an explosive bolt or damages a robotic arm by moving it too fast. All in all, space isn’t a very friendly environment for electronics or humans.

Figure 1: Space is a harsh environment for humans and electronics systems. (Mouser Electronics)

Designing Electronics Systems for Harsh Environments

At first glance, it seems like it would be virtually impossible to design electronics systems to operate correctly, billions of times a second, in such a harsh environment. For example, if you are subject to single event upset (SEU) strikes that can change the state of SRAM cells in an MCU or FPGA, what can you do about it? Luckily it turns out that these types of strikes don’t happen very often, allowing circuits to perform correctly for a majority of the time. There are some techniques designers should consider, however, to mitigate the disastrous effects an SEU-induced failure could create.

Mitigating SRAM-based SEU Strikes

One simple approach is to minimize the use of the more vulnerable elements in a device. For example, if the MCU uses a cache memory, it might best to bypass it. Cache memory is often designed for maximum speed and minimum size, which means they don't hold much charge. Design engineers can also minimize the amount of SRAM used in applications. Registers, accumulators, and peripheral buffer memories are sometimes designed using latches, which can be much more resistant to SEU strikes. Understanding where the vulnerable elements of a device are can often buy a significant improvement in defending designs from SEUs.

However, designers do need to use some SRAM in designs, so there are some techniques to use in order to determine if memory has been hit by an SEU strike. Some MCUs support parity detection on SRAMs, allowing design engineers to determine if a bit is in error. Even more useful is an SRAM with built-in error detection and correction. By adding a few more bits to each word, engineers can actually correct any single-bit error or detect any double-bit error. It seems counterintuitive that to increase reliability you want to increase the amount of SRAM, but it turns out that with error correction codes the investment really does pay off in dramatic improvements in reliability without noticeably impacting memory access time.

Another approach to mitigating SEU strikes in SRAM is to use block-based codes, such as those used in noisy communications environments, where fewer additional bits are needed but significant computation time is required. If an application has spare cycles and power, design engineers can implement a “scrubbing” operation in which periodic sweeps are made through SRAM to detect if any bits have been flipped. This won’t work in “real time like the more bit-hungry error detection and correction approach, but it can provide a significant increase in reliability if the data isn’t accessed very often (perhaps just being buffered between transmissions) and “real-time” access isn't required.

Mitigating FPGA-based SEU Strikes

In MCUs, design engineers can mitigate SRAM-based SEU strikes by minimizing SRAM use and by using error correction and detection techniques. In SRAM-based FPGAs the SRAM cells are distributed throughout the FPGA fabric to configure logic and routing resources. This makes it difficult to not use SRAM and very prohibitive to add error correction and detection circuitry. Some SRAM-based FPGAs provide support for “scrubbing” the configuration SRAM by periodically comparing it to the external non-volatile source of the configuration memory and flagging any changes. However, this can take a considerable amount of time, bandwidth, and power, so it isn’t possible in many applications.

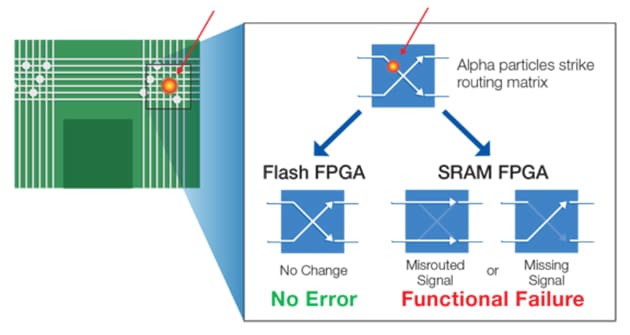

Another approach is to use an FPGA that doesn’t utilize SRAM configuration memory. The Microsemi / Microchip SmartFusion2 SoC FPGA, for example, uses flash configuration memory distributed throughout the FPGA fabric to configure logic and route signals. Flash memory is not susceptible to SEU-induced failures from alpha or neutron radiation, giving flash-based FPGAs dramatically improved reliability in environments where SEU effects are a concern.

Figure 2: Microsemi / Microchip SmartFusion2 Flash-based FPGAs are not susceptible to alpha/neutron failures, while SRAM-based FPGAs are. (Source: Microsemi / Microchip)

SmartFusion2 SoC FPGAs also utilize error detection and correction for the large-block SRAMs used for data storage and the large FIFOs used for the more complex peripherals mitigating SEU effects in these key blocks. Many of the small-storage elements used in simple peripherals are implemented through latches, instead of SRAM, making them less susceptible to SEU strikes, too. The on-chip external DDR memory controller even supports single-error correction and double-error detection, mitigating large external memories from SEU effects.

System Interconnect in Harsh Environments

Once you have your MCU or FPGA-based design optimized for a harsh environment, it needs to be connected to other sub-systems. Not only will temperature, pressure and radiation be a consideration for the interconnect system, but vibration and electromagnetic noise are also critically important. This will necessitate the use of special ruggedized connectors capable of transferring both signal and power within the same housing. The Phoenix Contact Heavycon EVO-D series is constructed of a special polyamide plastic material that offers high reliability in high vibration environments.

Figure 3: Amphenol 10G Ethernet fiber-to-copper connector and media converter. (Source: Amphenol)

Electromechanical Interfaces in Harsh Environments

At some point the system may need to control a servo or motor. The sensor used to determine position is perhaps the most critical component in the electromechanical control loop, so high reliability even in harsh environments is critical. Design engineers may not be able to use position sensors that rely on mechanical contacts because of the possibility of generating sparks or due to excessive wear that could reduce sensor lifetime. Hall-Effect sensors are a contactless technology that uses magnetic effects to determine rotational position. For example, the Vishay 34 THE servo Hall Effect sensor has a lifetime of over 50 M cycles with linearity of 0.5 percent. The convenient SPI output makes it easy to interface directly with MCUs or FPGAs.

Figure 4: Vishay Hall-Effect sensor for contactless electromechanical sensing.(Source: Vishay)

Conclusion

Space is one of the harshest environments around for humans or electronics systems. When designing systems for space or the upper atmosphere, the presence of high-energy particles makes it critical to mitigate single event upset (SEU) events by selecting the space components and using redundant design techniques that can help mitigate the effects of SEU events. Extremes of temperature, pressure, electromagnetic radiation, and vibration are also indicative of harsh environments, both in space and on (or under) the Earth. Electronics components and interconnect systems that are built to withstand these harsh environments are critical in keeping electronics systems from failing. You certainly don't want to be the one who gets called to go repair them.